Thiết kế phần cứng nhúng

THIẾT KẾ PHẦN CỨNG NHÚNG VỚI SỰ KẾT HỢP CÔNG NGHỆ

VI ĐIỀU KHIỂN – VI MẠCH LẬP TRÌNH SỐ

Ths. Đào Quang Khanh, Khoa Điện - Điện tử

Tóm tắt

Bài báo này trình bày một phương pháp thiết kế mạch nhúng với sự kết hợp hai công nghệ là công nghệ vi điều khiển và công nghệ vi mạch lập trình số. Cấu trúc phần cứng bao gồm một hệ thống vi điều khiển, các vi mạch chức năng đóng vai trò chính điều khiển, một hệ thống vi mạch lập trình số (PLD, SPLD, CPLD, FPGA) giữ vài trò thực hiện các chức năng giải mã địa chỉ, thực hiện cổng vào – ra số cho hệ thống, ghép nối truyền thông…Kết quả thực hiện trên mô phỏng trên phần mềm Proteus cho thấy hệ thống điều khiển được rút gọn về phần cứng, tính bảo mật của phần cứng được cao…, khi thực hiện trên mạch vật lý, thời gian lắp ráp linh kiện nhanh hơn, kích thước của bo mạch được thu gọn, chống nhiễu tốt.

1. Giới thiệu

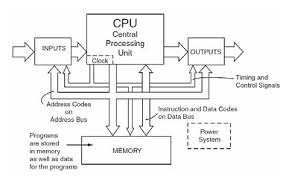

Hệ nhúng là một phần hệ thống xử lý thông tin nhúng trong các hệ thống lớn, phức hợp và độc lập ví dụ như trong ôtô, các thiết bị đo lường, điều khiển, truyền thông và thiết bị thông minh nói chung. Chúng là những tổ hợp của phần cứng và phần mềm để thực hiện một hoặc một nhóm chức năng chuyên biệt, cụ thể (Trái ngược với máy tính PC mà chúng ta thường thấy được sử dụng không phải cho một chức năng mà là rất nhiều chức năng hay phục vụ chung cho nhiều mục đích), cấu trúc một hệ thống nhúng sử dụng vi điều khiển/vi xử lý nhúng được thể hiện trên hình 1.1. [8]

Hình 1.1. Kiến trúc điển hình của các chip vi điều khiển/vi xử lý nhúng

Bài báo mô tả phương pháp tổng hợp mạch logic, cách thức thực hiện một mạch logic trên vi mạch lập trình số bằng phần mềm WinCupl. Việc tổng hợp mạch logic trên vi mạch lập trình số là thực hiện mạch chức năng phụ cho hệ thống vi điều khiển/vi xử lý nhúng như giải mã địa chỉ bộ nhớ, giải mã địa chỉ cổng, cổng logic vào ra số... Các tín hiệu số đầu vào cho mạch số tổ hợp là các tín hiệu địa chỉ, tín hiệu điều khiển ghép nối,…tín hiệu ra là các tín hiệu chọn chip, cho phép chip chức năng hoạt động…Hiệu quả của mạch số được thực hiện thông qua mạch mô phỏng trên phần mềm Proteus, mạch vật lý được thực hiện tại Phòng thí nghiệm Điện tử cơ bản của Khoa Điện – Điện tử Trường Cao đẳng công nghệ Viettronics.

2. Phương tiện và phương pháp

2.1. Phương tiện nghiên cứu

Các mạch chức năng phụ cho hệ vi điều khiển/vi xử lý nhúng thực hiện trong nghiên cứu này là vi mạch lập trình số GAL16V8(Atmel16V8), phần mềm lập trình vi mạch số là WinCupl. Hệ thống được kiểm nghiệm thông qua chương trình mô phỏng mạch điện tử Proteus và trên mạch vật lý.

2.2. Tổng hợp mạch logic trên vi mạch lập trình số

a. Tổng hợp mạch logic theo các biến vào – ra.

- Từ thiết kế một hệ vi điều khiển có mở rộng cổng vào-ra như sau:

Hình 2.1. Hệ vi điều khiển có mở rộng cổng vào- ra

- Hệ vi điều khiển có mở rộng cổng, yêu cầu các tín hiệu điều khiển theo bảng chân lý sau:

Bảng 2.1. Bảng chân lý tín hiệu điều khiển vào ra của hệ vi điều khiển

|

INPUT |

OUTPUT |

||||||||

|

A0 |

A1 |

A2 |

ALE |

/RD |

/WR |

LE1 |

LE2 |

/OE1 |

/OE2 |

|

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

|

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

|

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

|

1 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

- Hàm logic đầu ra của các tín hiệu điều khiển:

/OE1 = [(/A0A1/A2)ALE]+/RD, /OE2 = [(/A0A1A2)ALE]+/RD

LE1 = /[[(A0/A1A2)ALE] + /WR], LE2 = /[[(A0A1A2)ALE] + /WR]

b. Thực hiện trên vi mạch số

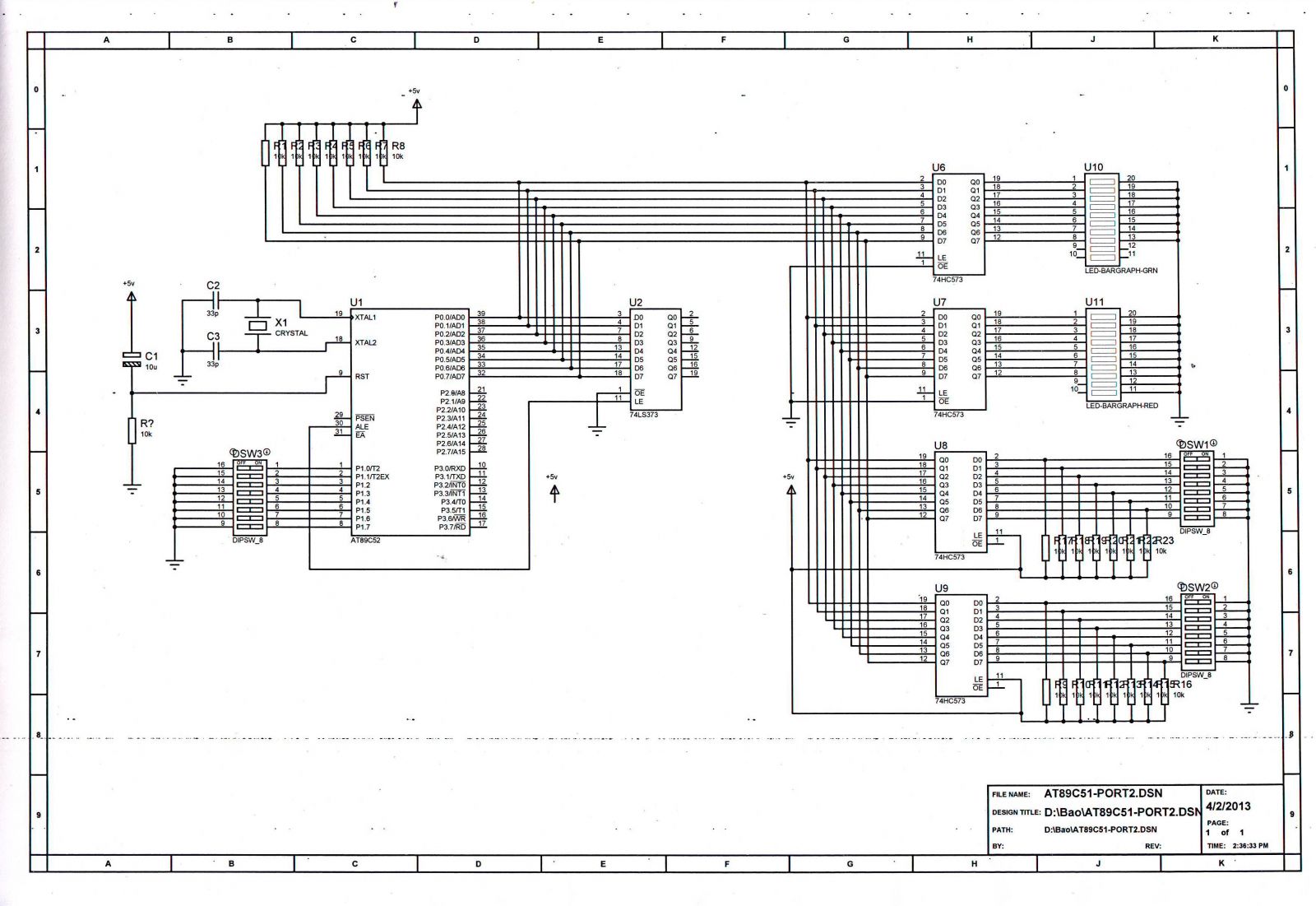

Trên cơ sở tổ hợp hàm logic của các tín hiệu điều khiển, sử dụng các cổng logic họ 74xx ta được sơ đồ hệ thống vi điều khiển có mở rộng cổng vào-ra như hình 2.2.

Hình 2.2. Thực hiện hàm logic bằng các cổng logic

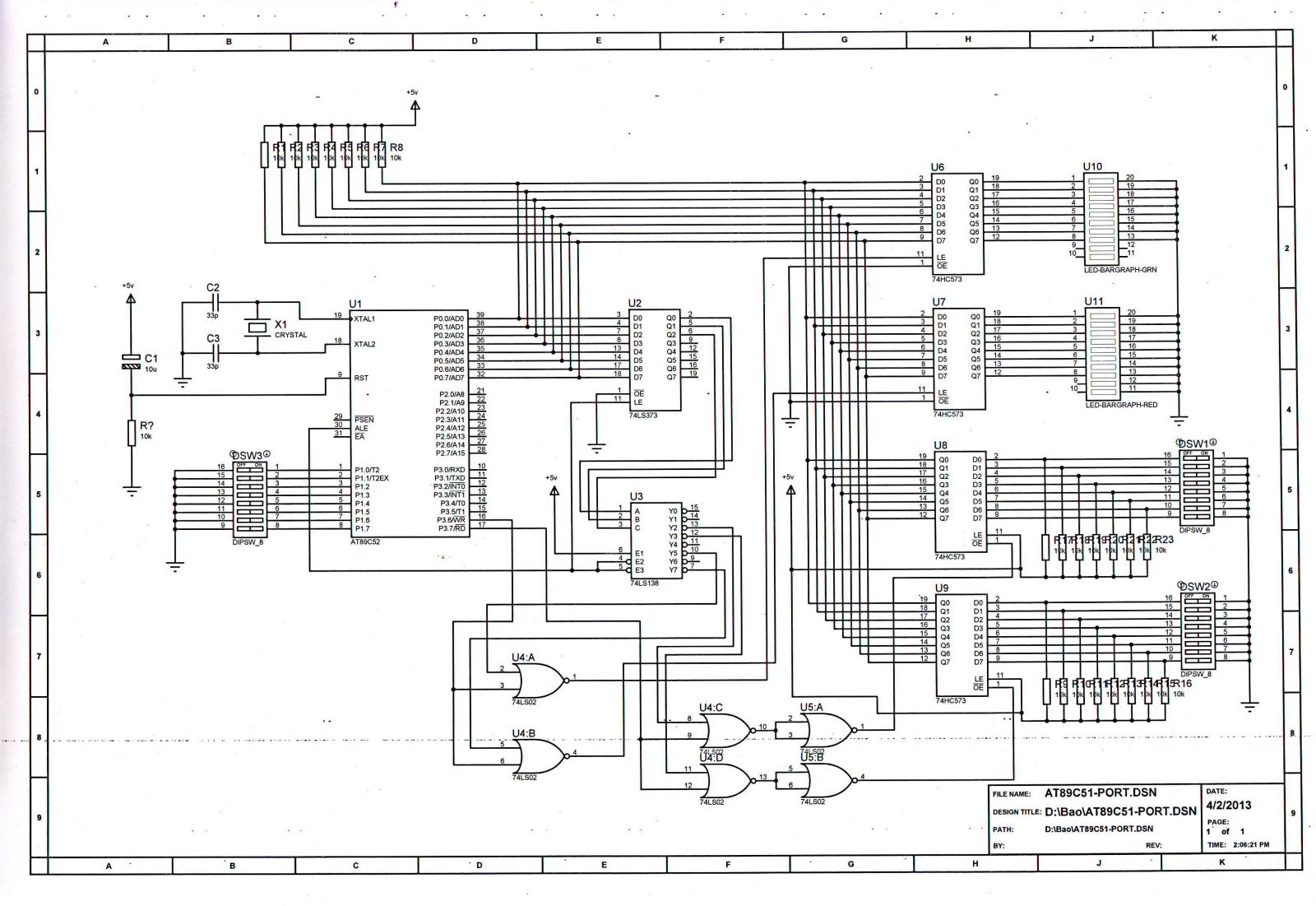

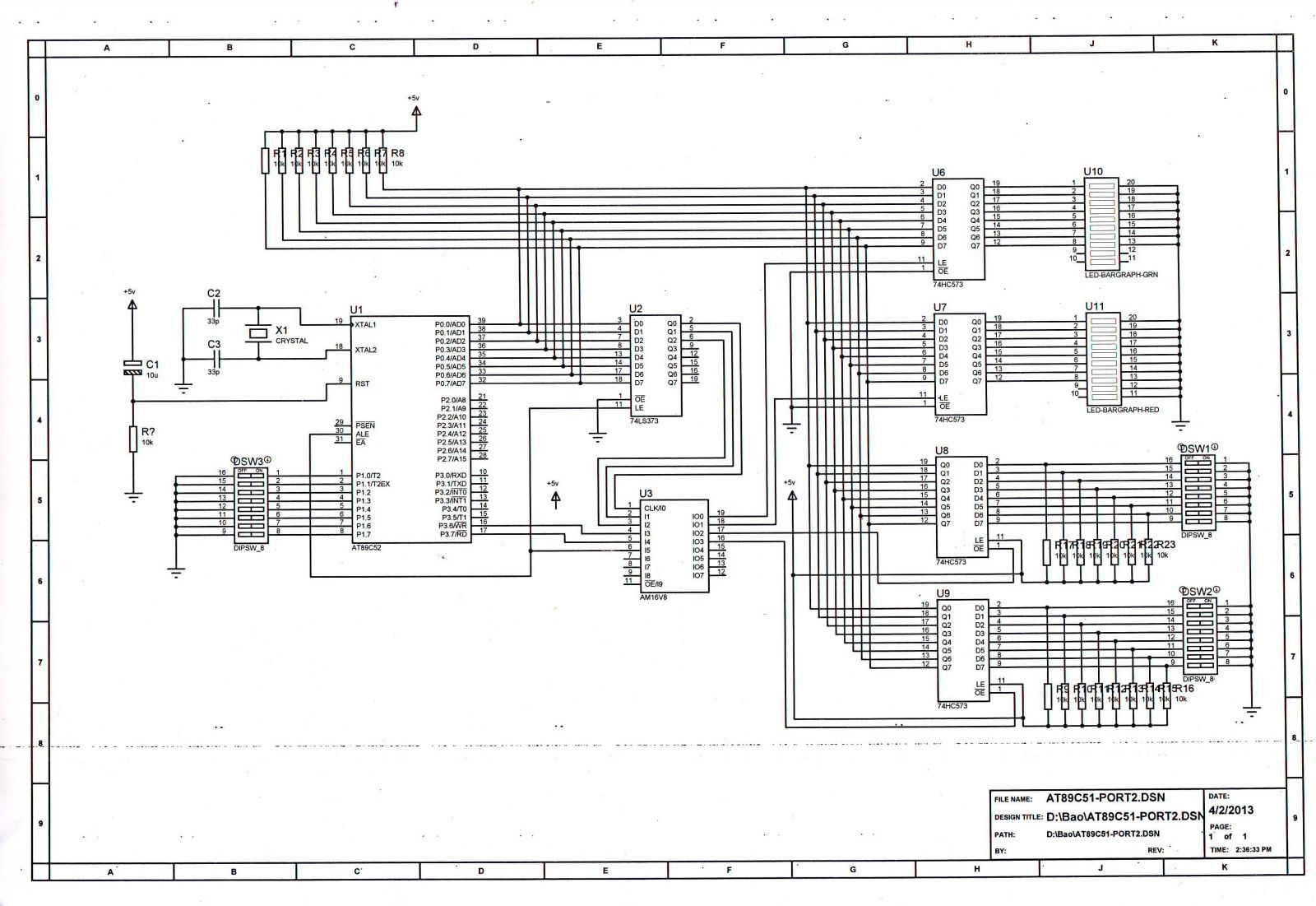

c. Thực hiện trên vi mạch lập trình số.

Bằng cách lập trình theo các tín hiệu vào ra bằng ngôn ngữ lập trình CUPL trên nền vi mạch lập trình số họ SPLD GAL16V8 thay thế cho các cổng logic họ 74xx, ta được sơ đồ như hình 2.3. [1]

Hình 2.3. Thực hiện hàm logic bằng vi mạch lập trình số loại SPLD(GAL16V8)

- Chương trình lõi cho vi mạch lập trình số GAL16V8:

/*************************************************************************/

NAME Decode 8051;

DATE 4/3/2013;

PARTNO ;

REVISION ;

DESIGNER Dao Quang Khanh;

COMPANY Truong Cao dang Cong nghe Viettronics;

ASSEMBLY ;

LOCATION ;

DEVICE g16v8;

/*************************************************************************/

/* Input and Output Pin Declarations */

/*************************************************************************/

PIN 2 = A0;

PIN 3 = A1;

PIN 4 = A2;

PIN 5 = ALE;

PIN 6 = _WR;

PIN 7 = _RD;

PIN 18 = LE2;

PIN 17 = OE1;

PIN 16 = OE2;

PIN 19 = LE1;

/*************************************************************************/

/* Logic Equations */

/*************************************************************************/

LE2 = !(Y5 # _WR);

LE1 = !(Y7 # _WR);

NetU13_O = !(Y2 # _RD);

NetU14_O = !(Y3 # _RD);

OE1 = !(NetU13_O # NetU13_O);

OE2 = !(NetU14_O # NetU14_O);

NetU17_O = !A0;

NetU18_O = !A1;

NetU19_O = !A2;

NetU20_O = !ALE;

Y2 = !(NetU17_O & A1 & NetU19_O & NetU20_O);

Y3 = !(A0 & A1 & NetU19_O & NetU20_O);

Y5 = !(A0 & NetU18_O & A2 & NetU20_O);

Y7 = !(A0 & A1 & A2 & NetU20_O);

/*************************************************************************/

- Chương trình cho vi điều khiển AT89C52:

INCLUDE 89c51.mc

Setup:

MOV R0,#5

MOV A,#0F0h

MOVX @R0,A

MOV R0,#7

MOVX @R0,A

Main:

MOV R0,#2

MOVX A,@R0

MOV R0,#5

MOVX @R0,A

MOV R0,#3

MOVX A,@R0

MOV R0,#7

MOVX @R0,A

SJMP Main

END

3. Kết quả thực nghiệm

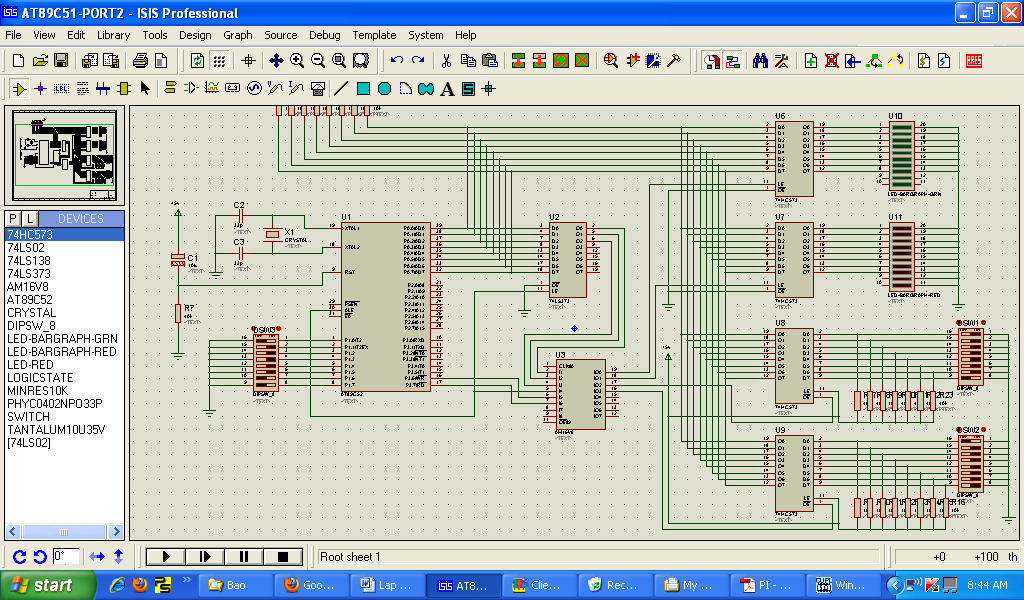

Hệ vi điều khiển có mở rộng cổng vào-ra như hình 2.2, hình 2.3 được mô phỏng trên phần mềm Proteus (hình 2.5), chương trình lõi cho vi mạch lập trình số GAL16V8 được soạn thảo và dịch bằng phần mềm WinCupl của Atmel (hình 2.4). Hệ thống trên hình 2.3 hoạt động chính xác tương tự như hệ thống hình 2.2. [4]

Hình 2.4. Chương trình lõi cho vi mạch GAL16V8 được thực hiện trên phần mềm WinCupl

Hình 2.5. Hệ thống vi điều khiển có mở rộng cổng vào ra có sử dụng vi mạch GAL 16V8 được mô phỏng bằng phần mềm Proteus

4. Kết luận

Bài báo mô tả phương pháp thiết kế mạch số trên nên công nghệ SPLD, công nghệ áp dụng đạt được một số ưu điểm sau:

- Khi thực hiện bằng các vi mạch số thông thường như họ 74xx, hệ thống hoạt động chính xác. Tuy nhiên, khi thực hiện bằng các vi mạch số họ 74xx hệ thống tồn tại một số nhược điểm sau:

+ Hệ thống cồng kềnh, phức tạp khi bảo trì sửa chữa

+ Tiêu tốn nhiều năng lượng điện

+ Độ bảo mật phần cứng không cao

+ Khả năng chống nhiều không tốt

- Khi thực hiện bằng các vi mạch lập trình số hệ thống hệ thống đã khắc phục được những nhược điểm của tồn tại của hệ thống sử dụng vi mạch số họ 74xx như sau:

+ Hệ thống được thu gọn, dễ bảo trì sửa chữa

+ Khi thực hiện trên mạch vật lý sẽ rút ngắn thời gian lắp ráp

+ Tiết kiệm năng lượng điện

+ Độ bảo mật phần cứng cao

Tài liệu tham khảo

[1] AMD (1996), PLD Design Basics

[2] AMD (1996), Combinatorial Logic Design

[3] ATMEL (2006), PLD Design Software Overview

[4] ATMEL – WinCUPL (2006), USER’S MANUAL

[5] Nguyễn Tăng Cương (2004), Cấu trúc và lập trình họ vi điều khiển 8051, NXB KH&KT

[6] Tổng Văn Ơn (2006), Thiết kế hệ thống với họ 8051, NXB Phương Đông

[7] LATTICE (2006), GAL®16V8 Device Datasheet

[8] Nguyễn Hồng Việt (2006), Hệ thống điều khiển nhúng, NXB Trường đại học Bách khoa Hà Nội.

Đã Xem: 3603

Bài Viết Mới Nhất

- Sinh viên khoa CNTT tham gia Hội thi sáng tạo trẻ VTC năm 2023

- Sinh viên khoa Kế toán tham gia Hội thi sáng tạo trẻ VTC năm 2023

- Sinh viên Khoa Điện - Điện tử tham gia Hội thi sáng tạo trẻ VTC, năm 2023

- Học ngành, nghề Điện công nghiệp

- Học sinh - sinh viên Khoa Điện - Điện tử tham dự Hội thi tay nghề giỏi VTC, năm 2021

- Cơ hội và thách thức cho sinh viên ngành kế toán trong cách mạng công nghiệp 4.0

.jpg)

.jpg)